Canali

Ultime news

Ultimi articoli

Le ultime dal Forum |

Correlati

Tag

Il pezzo che stai leggendo è stato pubblicato oltre un anno fa.

La trattazione seguente è piuttosto datata. Sebbene questo non implichi automaticamente che quanto descritto abbia perso di validità, non è da escludere che la situazione si sia evoluta nel frattempo. Raccomandiamo quantomeno di proseguire la lettura contestualizzando il tutto nel periodo in cui è stato proposto. La trattazione seguente è piuttosto datata. Sebbene questo non implichi automaticamente che quanto descritto abbia perso di validità, non è da escludere che la situazione si sia evoluta nel frattempo. Raccomandiamo quantomeno di proseguire la lettura contestualizzando il tutto nel periodo in cui è stato proposto.

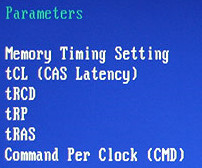

I timings sono i tempi di latenza che, insieme alla frequenza di clock, influiscono sulle velocità di trasferimento, e conseguente elaborazione, dei dati in memoria. Questi tempi vengono misurati in unità di cicli di clock (tempo che intercorre tra un segnale di clock ed un altro), che si presentano nel corso di operazioni di lettura/scrittura. Non tutti i tempi di latenza sono configurabili e dipendono strettamente dal tipo e dalla qualità dei chip/IC utilizzati per la costruzione del banco di RAM (a sua volta composto da un insieme di IC disposti come un array configurato, nei memory-kit di migliore qualità, in maniera bidimensionale/double side, altrimenti, in maniera monodimensionale/single side). Soventemente, al variare del vDimm (tensione che la mainboard determina automaticamente per il corretto funzionamento delle memorie in base agli standard Jedec, anche forzabile manualmente attraverso la configurazione dell'apposito voltaggio dal BIOS della propria scheda madre), in condizioni di overclock e a parità di frequenza di funzionamento delle RAM, è possibile (chip permettendo) ridurre i tempi di latenza accrescendo così la cosiddetta banda passante, meglio conosciuta come velocità di trasferimento (misurabile con appositi tool/benchmark). In senso contrario, è possibile rilassare (o anche lasciare inalterati) i timings per poi accrescere la frequenza di funzionamento dei moduli di memoria, agendo sui divisori resi disponibili dal memory controller del chipset/CPU installato sulla propria mainboard, e sulla frequenza di funzionamento del bus di sistema. Solitamente, il vDimm dell'array di chip che compongono il singolo banco di RAM viene riportato dal produttore attraverso una chiara etichetta posta sulla confezione del kit di memorie acquistato, o direttamente sul modulo stesso. Si sconsiglia, per uso quotidiano, di oltrepassare la soglia suggerita dal produttore e di ventilare dovutamente il comparto memorie in caso di overvolt. tCL-tRCD-tRP-tRAS & Command Rate

Queste strane sigle che ai più possono sembrare senza senso hanno una fondamentale importanza per la corretta configurazione delle memorie, andiamole ad analizzare nel dettaglio:

CAS# Latency Time (tCL)Indica il tempo che intercorre tra l'invio dell'istruzione per la lettura e l'attimo in cui il dato è pronto per la lettura stessa. A valori inferiori corrispondono performance superiori. RAS# To CAS# (Read/Write) Delay (tRCD)I dati immagazzinati nei chip di memoria vengono scritti e letti in righe e colonne. Per l'accesso viene specificato prima un Indirizzo di Riga e poi uno di Colonna. Il tRCD indica il tempo in cicli di clock che intercorre tra l'attivazione della riga e della colonna che identificano la cella di memoria elementare alla quale si andrà ad accedere. Minore sarà il Ras To Cas, più rapido sarà l'accesso ai dati. RAS# Precharge Time (tRP)È il tempo espresso in Cicli di Clock prima del quale il segnale Precharge (precaricamento dei condensatori di memoria) giunga ad una certa riga attiva, per disattivarla. Ancor più tecnicamente si può dire che il tRP è l'intervallo che intercorre tra i comandi RAS-Row Address Select (i comandi che seguono i Row Addres Select sono denominati Cas-Columns Address Select e sono necessari per la specificazione degli Indirizzi in Colonna; il segnale di Ras precede sempre quello di Cas) necessari per la specificazione degli Indirizzi di Riga. Cycle Time (tRAS)È l'intervallo di tempo necessario per individuare un dato in una cella di memoria elementare e renderlo disponibile. Command Rate (CR)Indica se i comandi vengono impartiti al chip di memoria, o ogni ciclo di clock, oppure ogni due cicli di clock (1T/2T). Conclusioni finaliSi può concludere che, in linea generale, e a parità di frequenza di clock, latenze minori corrispondono a performance maggiori, viceversa, timings più rilassati riducono la velocità di trasferimento e di conseguenza le performance generali del sistema. È importante ricordare che esistono anche altri tempi di latenza denominati sub-timings o alpha-timings, non meno importanti di quelli già riportati, ma non necessari per la configurazione ottimale delle vostre RAM (assumono grande rilievo nelle operazioni di fine-tuning nell'ambito dell'overclock). Segnala ad un amico |

- Unisciti a noi

- | Condizioni d'uso

- | Informativa privacy

- | La Redazione

- | Info

- | Pressroom

- | Contattaci

© Copyright 2025 BlazeMedia srl - P. IVA 14742231005

- Gen. pagina: 0.8 sec.

- | Utenti conn.: 102

- | Revisione 2.0.1

- | Numero query: 45

- | Tempo totale query: 0.28